มาลองทำเป็นขั้นตอนกัน

ทำไปตามลำดับของภาพนะ

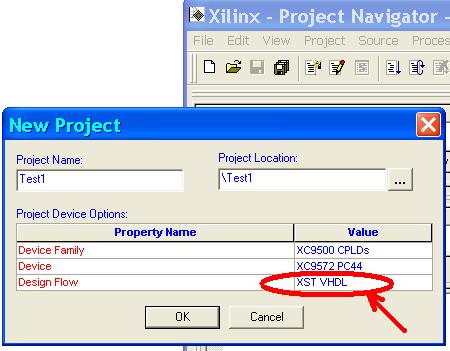

-------- 1 ---------------

เปิดโปรแกรม Xilinx ขึ้นมาแล้วเลือก File => New Project เลือก Device Family, Device และ Design Flow

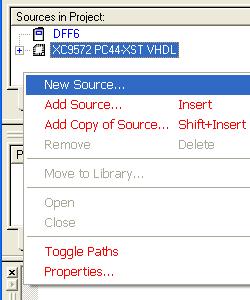

-------- 2 ---------------

คลิก ขวาในช่อง Sources in Project เลือก New Source....

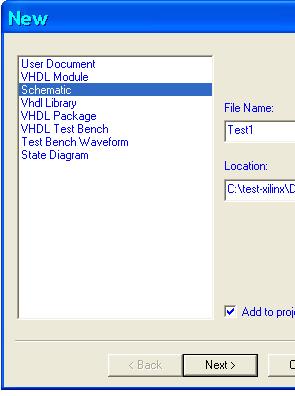

-------- 3 ---------------

เมื่อ window New เปิดขึ้นมาเลือก Schematic ใส่ชื่อ File Name และ Location.

Click เลือก Add to project

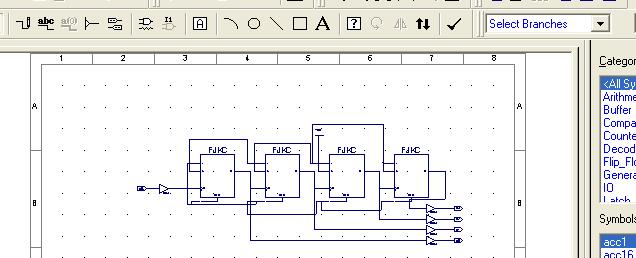

-------- 4 ---------------

(ลองดูแค่นี้ก่อนเด๊ยวไปจ่ายค่าโทรศัพท์ก่อนนะ)

เปิด file schematic แล้ววาดวงจรลงไป เสร็จแล้ว Save ด้วย

-------- 5 ---------------

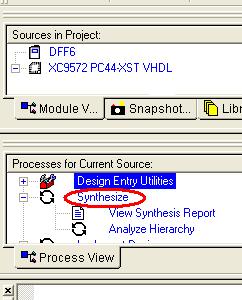

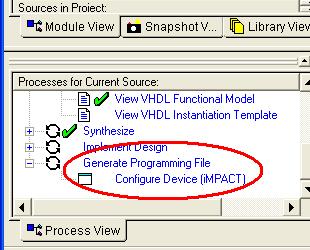

ที่ window Processes for Current Source.

Double click ที่ Synthesize

-------- 6 ---------------

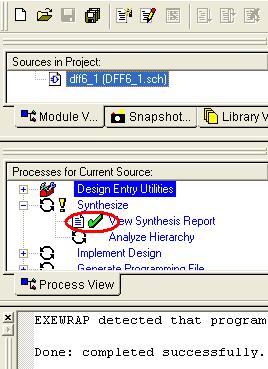

ถ้าวาดวงจรได้ถูกต้องจะมีเครื่องหมาย ถูก สีเขียว

ถ้าเป็นกากะบาดสีแดงก็แก้ไขส่วนที่ผิด

-------- 7 ---------------

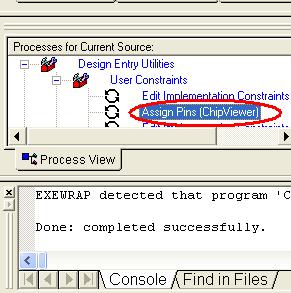

ขั้นต่อไป click + ที่หน้า Design Entry Utilities

click + ที่หน้า User Constraints

แล้ว double click ที่ Assign Pins

-------- 8 ---------------

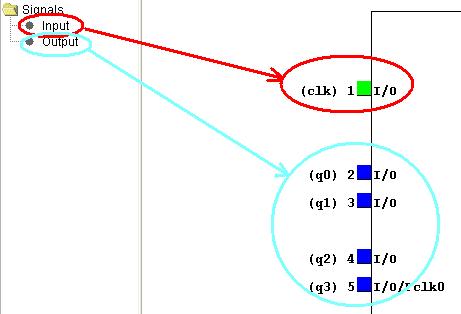

ใส่ขาตามชื่อที่เราตั้งไว้ตอนสร้าง New Project แล้ว click save

-------- 9 ---------------

click + ที่หน้า Generate Programming File (อยู่ด้านล่าง)

Double click Configure Device(iMPACT)

-------- 10 ---------------

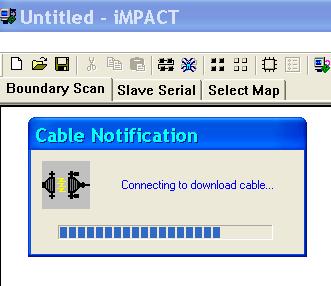

Program iMPACT จะถูกเปิดออกมา โปรแกรมจะ connect กับ download port อัตโนมัติ

-------- 11 ---------------

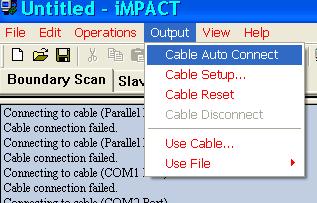

หรือจะมาที่ menu Output click Cable Auto Connect

-------- 12 ---------------

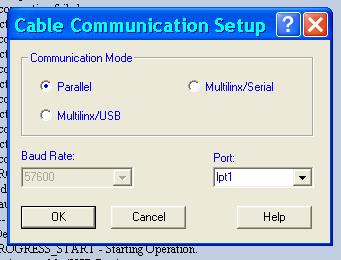

หรือจะเลือก Cable Setup เพื่อกำหนด port

-------- 13 ---------------

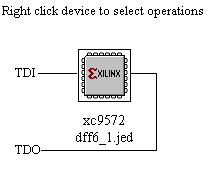

ถ้า connect สำเร็จ จะขึ้นรูป chip ขึ้นมา

-------- 14 ---------------

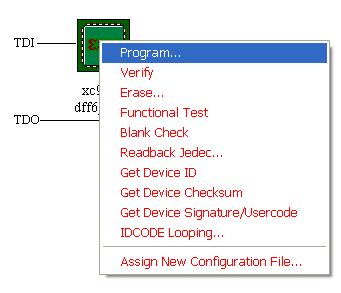

click ขวาที่ chip เลือก Program ที่ popup menu

-------- 15 ---------------

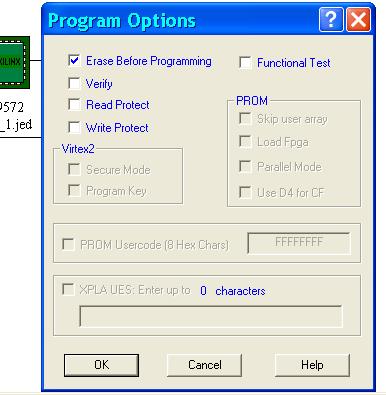

จะมี Window Program Options

เลือก Erase Before Programming

-------- 16 ---------------

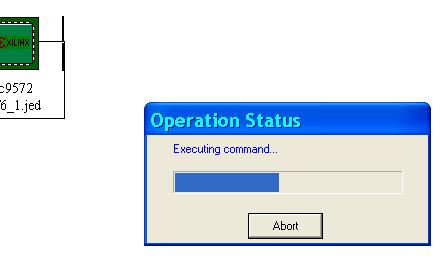

แสดงขณะกำลัง download program

-------- 17 ---------------

ในที่สุดก็สำเร็จ อย่าลืมไปต่อขาของ CPLD เพื่อทดสอบการทำงานด้วย

-------- 18 ---------------